# **UbiSwitch BaseBoard**

SFP+ and PicoClasp Daughterboard for UbiSwitch

MPN: BB-UD1-A-1

# **Datasheet**

February 2023

Board revision A

## **Contents**

| Contents                                              | 2  |

|-------------------------------------------------------|----|

| 1 General Information                                 | 3  |

| 1.1 Functionality and Features of UbiSwitch BaseBoard | 3  |

| 1.2 Safety Information                                | 4  |

| 1.3 Block Diagram                                     | 5  |

| 1.4 Included Equipment                                | 8  |

| 1.5 RoHS Compliance                                   | 8  |

| 2 Hardware Interfaces                                 | 9  |

| 2.1 Board Map                                         | 9  |

| 2.2 Connectors and Pinouts                            | 10 |

| 2.3 Other Interfaces                                  | 23 |

| 4 Device Configuration                                | 26 |

| 5 Mechanical drawing                                  | 27 |

| 6 Datasheet Changelog                                 | 28 |

| 7 Contact                                             | 28 |

## **1 General Information**

## 1.1 Functionality and Features of UbiSwitch BaseBoard

The BotBlox UbiSwitch Baseboard is a breakout system designed to provide a very compact (70mm x 70mm) plug and play system for UbiSwitch. UbiSwitch Baseboard provides 3 x 10Gbps on SFP+ cages and 8 x 1Gbps ethernet ports on Molex PicoClasp headers.

UbiSwitch Baseboard itself does not contain any ethernet switching silicon, rather it contains the necessary connectors and routing required to use UbiSwitch as a complete system. This includes three 10GBASE-R SFP+, and eight Molex PicoClasp headers for direct connection to an external system.

When used with UbiSwitch, UbiSwitch BaseBoard will automatically begin auto negotiation with any connected devices and begin receiving and forwarding frames as an unmanaged ethernet switch.

UbiSwitch BaseBoard runs from a wide input voltage range of 8V to 60V allowing integration into a wide range of applications.

#### 1.1.1 Features

The features described below apply when the board is used with UbiSwitch.

- 3 x 10GBASE-R ethernet ports

- 8 x 10/100/1000BASE-T ethernet ports

- Input voltage range from 8V to 60V

- 69.8mm x 69.8mm board size

- Positive Locking Molex PicoClasp connectors for power and Ethernet ports

- SFP+ connector for 10G capable SFPs

#### 1.1.2 General Information

| Voltage Input         | 8V to 60V DC                                |

|-----------------------|---------------------------------------------|

| Supported Protocols   | 10BASE-T, 100BASE-TX, 1000BASE-T, 10GBASE-R |

| Power Consumption     | 7.2W (idle)                                 |

| Weight                | 60 grams                                    |

| Size                  | 69.8mm x 69.8mm x 18mm (without heatsink)   |

| Operating Temperature | -40°C to +85°C                              |

| Storage Temperature   | -40°C to +125°C                             |

Table 1: General Information

#### 1.1.3 General Operating Instructions

UbiSwitch Baseboard is designed for use in harsh environments, operating from a nominal supply voltage of 24V, but with the ability to operate from as low as 8V and as high as 60V. UbiSwitch Baseboard is purely a breakout board, and contains no switching capabilities by itself. It must be used with UbiSwitch to create a full ethernet switch system.

To use UbiSwitch Baseboard, first mate the board with UbiSwitch then apply an input voltage from 8 to 60V. Then connect external devices and the Ubi system will begin functioning as an unmanaged switch with up to 3 x 10GBASE-R SFP+ ports and 8 x 1GBASE-T ports.

## 1.2 Safety Information

- This device can operate on voltages near and above 60V. Please read this manual before operating.

- This device is fully functionally tested prior to shipment however in-application testing prior to integration is recommended.

- This device is provided as an electronic circuit board, and requires integration into chassis for full ingress protection.

- Do not use this product in wet environments without integrating into a chassis.

- Do not operate this product beyond the rated temperature and voltages.

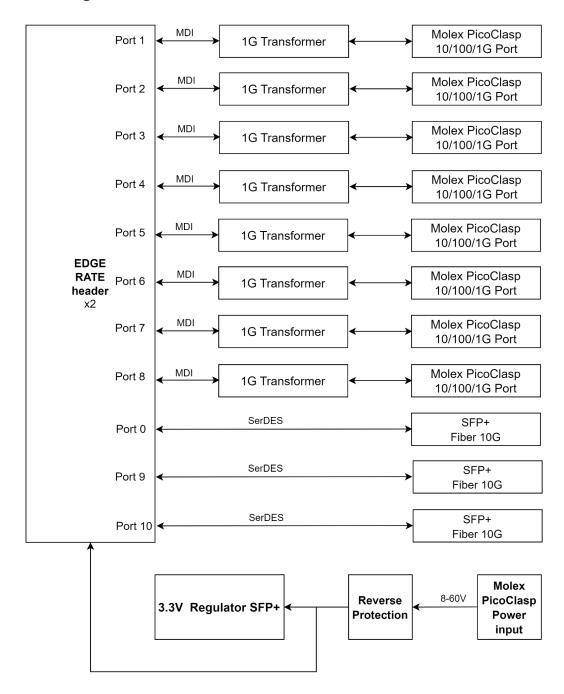

## 1.3 Block Diagram

Figure 1: UbiSwitch Baseboard Block Diagram

#### 1.3.1 System Design

To understand how UbiSwitch and UbiSwitch Baseboard work together, it is necessary to understand the UbiSwitch design. While the UbiSwitch has its own datasheet, a brief explanation is provided here.

UbiSwitch contains the main ethernet switch IC. This IC provides eight 1GBASE-T ethernet ports and three 10Gbps 10GBASE-R ports. These eleven ports are routed directly to a Samtec Egde Rate connector on UbiSwitch, along with a number of other power and control lines.

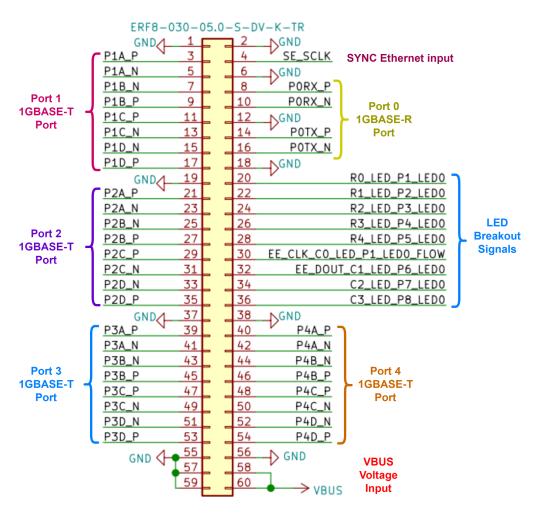

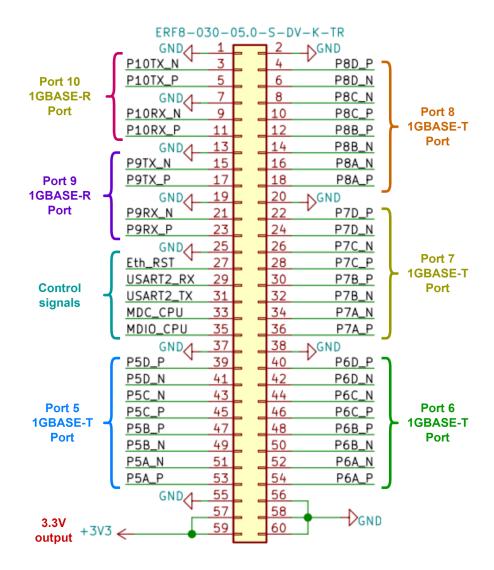

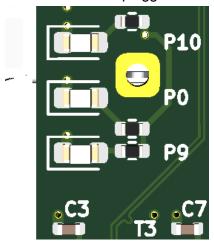

Figures 2 and 3 below show the signals carried on the UbiSwitch board.

Figure 2: Signals on the UbiSwitch carried on the Samtec Edge Rate header 1

\$

Figure 3: Signals on the UbiSwitch carried on the Samtec Edge Rate header 2

The signals shown in Figure 2 and Figure 3 enter UbiSwitch Baseboard through its corresponding Samtec EdgeRate header. UbiSwitch Baseboard then routes these signals in the following ways.

- Ports 1-8 (the 10/100/1GBASE-T ports) are routed to Molex PicoClasp headers through ethernet magnetics.

- Ports 0, 9 and 10 (the 10GBASE-R ports) are routed to 1x3 SFP+ connector.

- UbiSwitch Baseboard houses a Molex PicoClasp header for 8-60V power input (VBus). This is then routed to the Samtec Edge Rate header to power the UbiSwitch.

- Serial signals are routed to a Molex PicoClasp header.

- SMI signals are routed to a Molex PicoClasp header.

- LED signals are routed to a Molex PicoClasp header.

In this way UbiSwitch Baseboard provides physical access to the 1GBASE-T ports and 10GBASE-R from UbiSwitch.

### 1.3.2 Auto negotiation

All ports on the UbiSwitch system support auto negotiation, auto-MDI/MDIX and polarity correction. Each port will auto negotiate with the connected device to achieve the fastest possible speed. The fastest possible speed will depend on what the connected device is capable of, and the quality of the cabling between UbiSwitch Baseboard and the connected device. This simplifies system connectivity, meaning eight of the ports on UbiSwitch Baseboard are compatible with any 10/100/1G device and three ports are compatible with Fiber SFP+ devices. For more information on this, see section 2.4 on the UbiSwitch datasheet.

## 1.4 Included Equipment

The product includes the following:

- 1 x UbiSwitch Baseboard board

- 8 x Molex PicoClasp to RJ45 4-way Shielded Twisted Pair cables (300mm)

- 1 x Molex PicoClasp Power Cable to bare, tinned leads (300mm)

## 1.5 RoHS Compliance

The BotBlox UbiSwitch Baseboard complies with the RoHS (Restriction of Hazardous Substances Directive) Certificate of Compliance.

## 2 Hardware Interfaces

## 2.1 Board Map

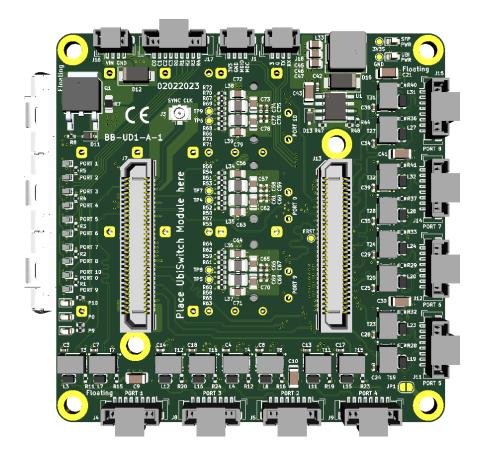

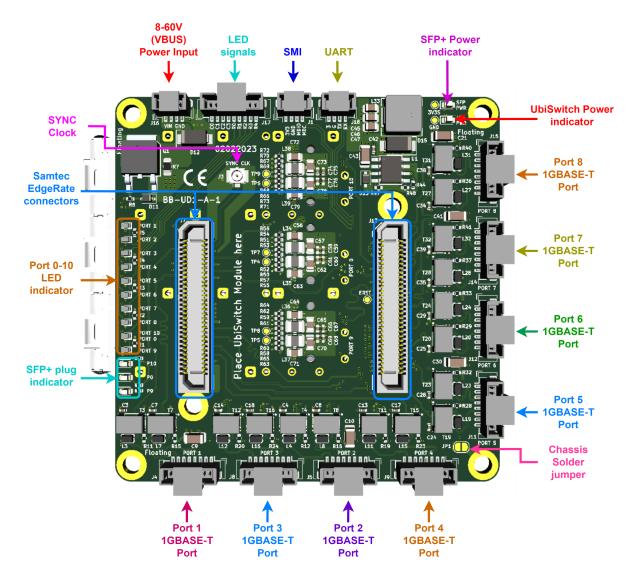

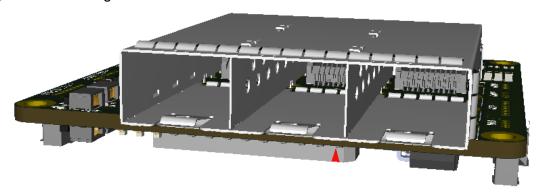

Figure 4: UbiSwitch Baseboard Board Map (front)

Figure 5: UbiSwitch Baseboard Board Map (back)

## 2.2 Connectors and Pinouts

### 2.2.1 Edge Rate connector

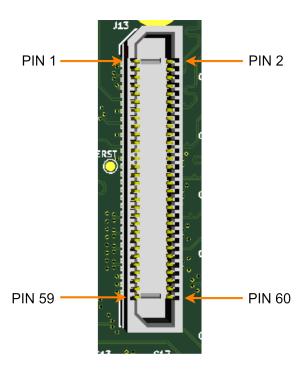

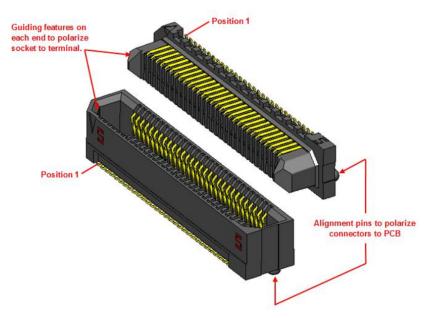

The 8 ports, 3 SerDES, SMI, LED signals, UART, input voltage and output voltage are placed onto a Samtec Edge Rate™ (MPN: <u>ERF8-030-05.0-S-DV-K-TR</u>) stackable header. The Edge Rate connector on the UbiSwitch Baseboard Board is shown in figure 6 below.

Figure 6: Edge Rate connector on UbiSwitch Baseboard

Mating part: <u>ERM8-030-02.0-S-DV-TR</u> (used on UbiSwitch) The mating method is shown in figure 7 below.

Figure 7: Edge Rate connector mating

The signal to pin assignments used on UbiSwitch Baseboard is detailed in table 3 and table 4 below.

| Connector | Pin name | Pin<br>number | Description                                                                               |

|-----------|----------|---------------|-------------------------------------------------------------------------------------------|

| J7        | GND      | 1             | Ground                                                                                    |

|           | GND      | 2             | Ground                                                                                    |

|           | GND      | 6             | Ground                                                                                    |

|           | GND      | 12            | Ground                                                                                    |

|           | GND      | 18            | Ground                                                                                    |

|           | GND      | 19            | Ground                                                                                    |

|           | GND      | 37            | Ground                                                                                    |

|           | GND      | 38            | Ground                                                                                    |

|           | GND      | 55            | Ground                                                                                    |

|           | GND      | 56            | Ground                                                                                    |

|           | GND      | 57            | Ground                                                                                    |

|           | GND      | 59            | Ground                                                                                    |

|           | VBUS     | 58            | Input supply voltage, 8V to 60V                                                           |

|           | VBUS     | 60            | Input supply voltage, 8V to 60V                                                           |

|           | P1A_P    | 3             | Port 1 1000BASE-T Differential Data Pair A ~ D<br>Note: 100BASE-TX and 10BASE-Te are also |

|           | P1A_N    | 5             | supported on the A and B pairs.                                                           |

|           | P1B_P    | 9             |                                                                                           |

|           | P1B_N    | 7             |                                                                                           |

|           | P1C_P    | 11            |                                                                                           |

|           | P1C_N    | 13            |                                                                                           |

|           | P1D_P    | 17            |                                                                                           |

|           | P1D_N    | 15            |                                                                                           |

| P |        |    | 1                                                                       |

|---|--------|----|-------------------------------------------------------------------------|

|   | P2A_P  | 21 | Port 2 1000BASE-T Differential Data Pair A ~ D                          |

|   | P2A_N  | 23 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

|   | P2B_P  | 27 |                                                                         |

|   | P2B_N  | 25 |                                                                         |

|   | P2C_P  | 29 |                                                                         |

|   | P2C_N  | 31 |                                                                         |

|   | P2D_P  | 35 |                                                                         |

|   | P2D_N  | 33 |                                                                         |

|   | P3A_P  | 39 | Port 3 1000BASE-T Differential Data Pair A ~ D                          |

|   | P3A_N  | 41 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

|   | P3B_P  | 45 |                                                                         |

|   | P3B_N  | 43 |                                                                         |

|   | P3C_P  | 47 |                                                                         |

|   | P3C_N  | 49 |                                                                         |

|   | P3D_P  | 53 |                                                                         |

|   | P3D_N  | 51 |                                                                         |

|   | P4A_P  | 40 | Port 4 1000BASE-T Differential Data Pair A ~ D                          |

|   | P4A_N  | 42 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

|   | P4B_P  | 46 |                                                                         |

|   | P4B_N  | 44 |                                                                         |

|   | P4C_P  | 48 |                                                                         |

|   | P4C_N  | 50 |                                                                         |

|   | P4D_P  | 54 |                                                                         |

|   | P4D_N  | 52 |                                                                         |

|   | P0TX_P | 14 | SerDES Port 0 Transmit Data bus positive                                |

|   | P0TX_N | 16 | SerDES Port 0 Transmit Data bus negative                                |

|   |        |    |                                                                         |

| P0RX_P  | 8  | SerDES Port 0 Receive Data bus positive                                                                                                                                                                                                        |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0RX_N  | 10 | SerDES Port 0 Receive Data bus negative                                                                                                                                                                                                        |

| R0_LED  | 20 | Parallel multiplexed LED outputs. These active low                                                                                                                                                                                             |

| R1_LED  | 22 | LED pins directly drive the port's LEDs supporting a range from 1 to 20 LEDs in a multiplexed fashion. In                                                                                                                                      |

| R2_LED  | 24 | this mode the cathode of each LED connects to these pins through a series current limiting resistor.                                                                                                                                           |

| R3_LED  | 26 | The anode of each LED connects to one of the Cx_LED pins below                                                                                                                                                                                 |

| R4_LED  | 28 |                                                                                                                                                                                                                                                |

| C0_LED  | 30 | connect to the anode of LED column 0 for each row                                                                                                                                                                                              |

| C1_LED  | 32 | connect to the anode of LED column 1 for each row                                                                                                                                                                                              |

| C2_LED  | 34 | connect to the anode of LED column 2 for each row                                                                                                                                                                                              |

| C3_LED  | 36 | connect to the anode of LED column 3 for each row                                                                                                                                                                                              |

| SE_SCLK | 2  | Synchronous Ethernet Source Clock. This is a 25 MHz reference clock which can be used as a synchronous clock input from the board or system. This signal must come from a high quality clock conditioning circuit or Synchronous Ethernet PLL. |

Table 2: UbiSwitch Baseboard J7 connector pin assignments

| Connector | Pin name | Pin<br>number | Description |

|-----------|----------|---------------|-------------|

| J13       | GND      | 1             | Ground      |

|           | GND      | 2             | Ground      |

|           | GND      | 7             | Ground      |

|           | GND      | 13            | Ground      |

|           | GND      | 19            | Ground      |

|           | GND      | 20            | Ground      |

|           | GND      | 25            | Ground      |

|           | GND      | 37            | Ground      |

| GND   | 38 | Ground                                                                  |

|-------|----|-------------------------------------------------------------------------|

| GND   | 55 | Ground                                                                  |

| GND   | 56 | Ground                                                                  |

| GND   | 58 | Ground                                                                  |

| GND   | 60 | Ground                                                                  |

| +3V3  | 57 | Output 3.3V, maximum 0.5A                                               |

| +3V3  | 59 | Output 3.3V, maximum 0.5A                                               |

| P5A_P | 53 | Port 5 1000BASE-T Differential Data Pair A ~ D                          |

| P5A_N | 51 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

| P5B_P | 47 |                                                                         |

| P5B_N | 49 |                                                                         |

| P5C_P | 45 |                                                                         |

| P5C_N | 43 |                                                                         |

| P5D_P | 39 |                                                                         |

| P5D_N | 41 |                                                                         |

| P6A_P | 54 | Port 6 1000BASE-T Differential Data Pair A ~ D                          |

| P6A_N | 52 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

| P6B_P | 48 |                                                                         |

| P6B_N | 50 |                                                                         |

| P6C_P | 46 |                                                                         |

| P6C_N | 44 |                                                                         |

| P6D_P | 40 |                                                                         |

| P6D_N | 42 |                                                                         |

| P7A_P | 36 | Port 7 1000BASE-T Differential Data Pair A ~ D                          |

| P7A_N | 34 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |

| P7B_P | 30 |                                                                         |

|       |    |                                                                         |

| P7B_N   | 32 |                                                                                                                                                                                                                                                                                                                                                      |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P7C_P   | 28 |                                                                                                                                                                                                                                                                                                                                                      |

| P7C_N   | 26 |                                                                                                                                                                                                                                                                                                                                                      |

| P7D_P   | 22 |                                                                                                                                                                                                                                                                                                                                                      |

| P7D_N   | 24 |                                                                                                                                                                                                                                                                                                                                                      |

| P8A_P   | 18 | Port 8 1000BASE-T Differential Data Pair A ~ D                                                                                                                                                                                                                                                                                                       |

| P8A_N   | 16 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs.                                                                                                                                                                                                                                                                              |

| P8B_P   | 12 |                                                                                                                                                                                                                                                                                                                                                      |

| P8B_N   | 14 |                                                                                                                                                                                                                                                                                                                                                      |

| P8C_P   | 10 |                                                                                                                                                                                                                                                                                                                                                      |

| P8C_N   | 8  |                                                                                                                                                                                                                                                                                                                                                      |

| P8D_P   | 4  |                                                                                                                                                                                                                                                                                                                                                      |

| P8D_N   | 6  |                                                                                                                                                                                                                                                                                                                                                      |

| P9TX_P  | 17 | SerDES Port 9 Transmit Data bus positive                                                                                                                                                                                                                                                                                                             |

| P9TX_N  | 15 | SerDES Port 9 Transmit Data bus negative                                                                                                                                                                                                                                                                                                             |

| P9RX_P  | 23 | SerDES Port 9 Receive Data bus positive                                                                                                                                                                                                                                                                                                              |

| P9RX_N  | 21 | SerDES Port 9 Receive Data bus negative                                                                                                                                                                                                                                                                                                              |

| P10TX_P | 5  | SerDES Port 10 Transmit Data bus positive                                                                                                                                                                                                                                                                                                            |

| P10TX_N | 3  | SerDES Port 10 Transmit Data bus negative                                                                                                                                                                                                                                                                                                            |

| P10RX_P | 11 | SerDES Port 10 Receive Data bus positive                                                                                                                                                                                                                                                                                                             |

| P10RX_N | 9  | SerDES Port 10 Receive Data bus negative                                                                                                                                                                                                                                                                                                             |

| ETH_RST | 27 | Active low system reset                                                                                                                                                                                                                                                                                                                              |

| MDC_CPU | 33 | Management Data Clock, Slave. MDC_CPU is the reference clock input for the serial management interface (SMI) that connects to an external SMI master, typically a CPU. A continuous clock stream is not expected. The maximum frequency supported is 20.0 MHz The CPU's SMI interface is used to access the device's registers but it cannot be used |

|           |    | until the device's INTn pin becomes active low.                                                                            |

|-----------|----|----------------------------------------------------------------------------------------------------------------------------|

| MDIO_CPU  | 35 | Management Data I/O, Slave. MDIO_CPU is used to transfer management data in and out of the device synchronously to MDC_CPU |

| USART2_RX | 29 | Microcontroller USART RX line                                                                                              |

| USART2_TX | 31 | Microcontroller USART TX line                                                                                              |

Table 3: UbiSwitch Baseboard J13 connector pin assignments

#### 2.2.2 SFP+ connector

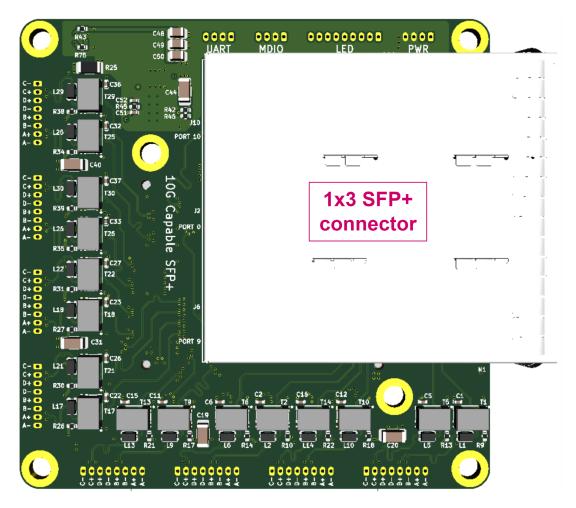

UbiSwitch Baseboard supports 3x10Gbps Fiber SFP+ module. To achieve a very small form factor, a 1x3 SFP+ cage is used.

Figure 8: 1x3 SFP+ connector on UbiSwitch Baseboard

At present, only 10G capable SFPs can be used with UbiSwitch Baseboard. This is because these three ports are, by default, configured with a 10GBASE-R interface. This means you should use a 10G SFP, such as the <u>Cisco SFP-10G-T-X module</u>.

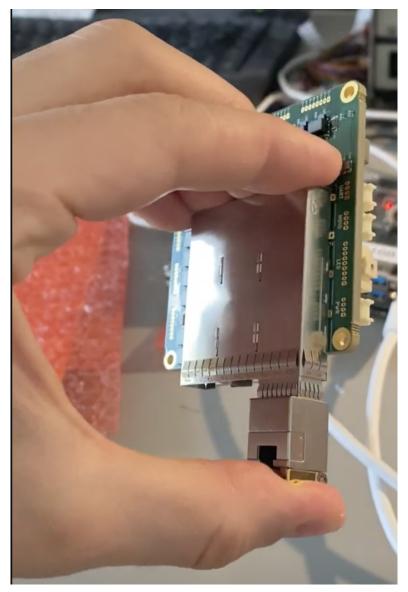

Please note that these cages can occasionally be quite stiff on initial insertion of an SFP. This is usually only the case on the first or second insertions, and the cages will become more compliant over time. This means you may need to apply a fair amount of force upon first insertion. To apply this force without damaging the delicate transformers on the board, see figure 9 below. A video demonstration can be found at the link below.

https://www.youtube.com/shorts/VFnaphZ vT4

Figure 9: How to insert an SFP into the SFP cage without risking damage to any components on the board.

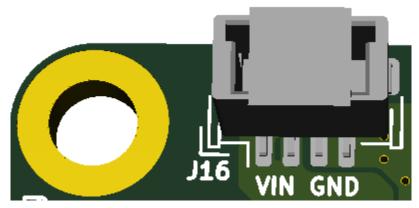

### 2.2.3 Voltage Input

The top left connector is the voltage input terminal. A four pin PicoClasp connector is used to allow the input voltage to be easily daisy chained between boards (two wires per power rail).

The voltage input has the following features:

- Voltage input can range from 8 to 60V

- Maximum allowable voltage of 65V

- Transient voltage protection above 66.3V

- Reverse polarity protection

The pinout of the voltage input connector is shown in figure 10 below.

Figure 10: Voltage input header pinout

## Connector part numbers

| Connector on board | Mating header | Crimp used | Wire used     |

|--------------------|---------------|------------|---------------|

| 5019400407         | 5019390400    | 5013340000 | UL1061, 28AWG |

Table 4: Voltage input connector pinout and part numbers

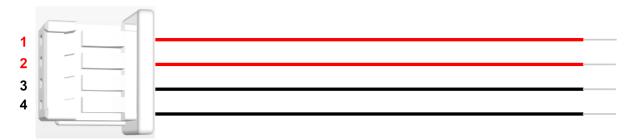

## Cable pinout

Figure 11: Voltage input cable pinout (red = V+, black = GND)

#### 2.2.4 Ethernet Ports

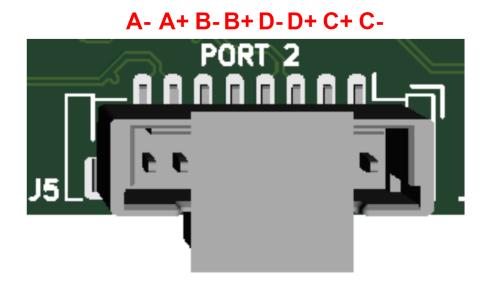

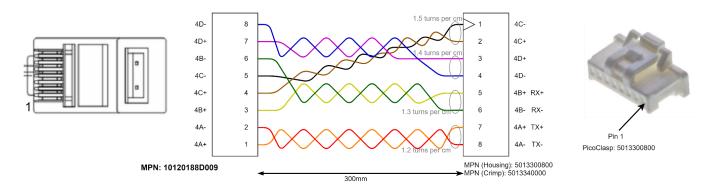

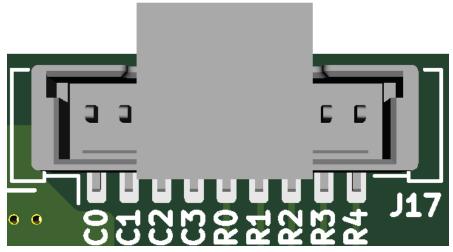

There are eight ethernet connectors on UbiSwitch Baseboard. Each connector has eight pins corresponding to the eight signals required for 1000BASE-T which are A-, A+, B-, B+, D-, D+, C+, C-. The pin mapping of all eight connectors is identical.

Figure 12: Ethernet port pinout

| Connector on board | Mating header | Crimp used | Wire used     |

|--------------------|---------------|------------|---------------|

| <u>5013310807</u>  | 5013300800    | 5013340000 | UL1061, 28AWG |

Table 5: Ethernet connector pinout and part numbers

Figure 13: Ethernet cable pinout

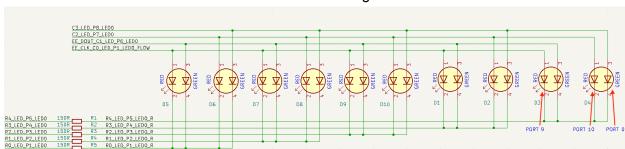

#### 2.2.5 External LED Header

An External LED header on the top of the board allows port activity indicator signals can be brought off-board for integration into a chassis

Figure 14: External LED header pinout

| Connector on board | Mating header | Crimp used        | Wire used     |

|--------------------|---------------|-------------------|---------------|

| 5013310907         | 5013300900    | <u>5013340000</u> | UL1061, 28AWG |

Table 6: Ethernet connector pinout and part numbers

### External LEDs connection should be followed below diagram:

Figure 15: External LEDs connection

Ports 1 to 8 use two LED signals to indicate link speed and activity. In figure 14 above, these two LED signals are mapped to a dual color LED, but this could alternatively be two single color LEDs. In figure 14 above, the color corresponds to the link speed and activity is shown via blinking. (Green blinking indicates a 1000 Mbps connection, Red blinking indicates a 100Mbps connection, Orange blink indicates a 10Mbps connection). A solid on LED indicates Link/No Activity.

Ports 0, 9 and 10 each use a single LED signal to indicate activity. In the diagram above, Port 10 uses the red part of a dual color LED while Port 0 uses the green part of a dual color LED to save space. Port 9 uses the red reen part of another dual color LED.

$150\Omega$  resistors are embedded onto the board and hence will already be in series with any external LEDs. This means that additional series resistors may not need to be added to any external LEDs.

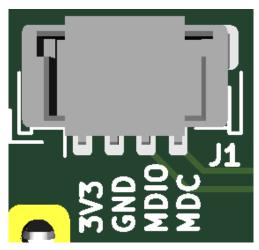

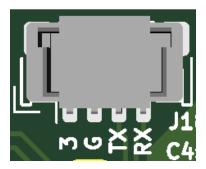

#### 2.2.6 SMI header

The SMI header on the top of the board allows access to the registers of Switch IC on the UbiSwitch module. We do not recommend using the SMI header for switch configuration. Instead, use the serial header.

Figure 16: SMI header pinout

| Connector on board | Mating header | Crimp used | Wire used     |

|--------------------|---------------|------------|---------------|

| 5019400407         | 5019390400    | 5013340000 | UL1061, 28AWG |

Table 7: SMI connector and part numbers

#### 2.2.7 Serial header

The serial header allows control messages to be sent/received to/from the microcontroller on UbiSwitch to configure the device. This allows the user to wire any external serial device to UbiSwitch Baseboard, and send serial commands to the system to provide switch configuration. For more information on this, see section 2.4.3 of the UbiSwitch datasheet.

Figure 17: UART header pinout

| Connector on board | Mating header | Crimp used | Wire used     |

|--------------------|---------------|------------|---------------|

| 5019400407         | 5019390400    | 5013340000 | UL1061, 28AWG |

Table 8: UART connector and part numbers

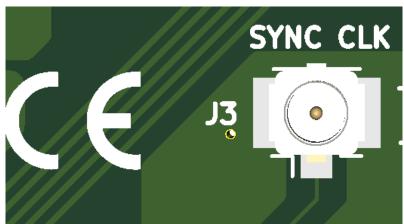

### 2.2.8 Synchronous Ethernet Source Clock IPEX header

An IPEX header on the board allows use of the Synchronous Ethernet Source Clock feature. This is a 25 MHz reference clock which can be used as a synchronous clock input to UbiSwitch. This signal must come from a high quality clock conditioning circuit or Synchronous Ethernet PLL. To fully use this feature requires that it be set up in software. By default, this clock is not used.

Figure 18: IPEX header

#### 2.3 Other Interfaces

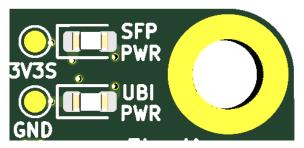

#### 2.3.1 LEDs

There are 15 LEDs on UbiSwitch Baseboard in total. Ten of these LEDs are dual color LEDs, meaning there are a total of twenty-five LED signals on this board. Ten of the LED signals can be taken off board.

The 3.3V SFP+ Power Indicator LED (**Green**) indicates that voltage is present on the 3.3V SFP+ line. It should be solid green in normal operation.

The 3.3V UBI Power Indicator LED (**Green**) indicates that 3.3V of the UbiSwitch module is present. That means the UbiSwitch is stacked on the UbiSwitch Baseboard board correctly and both of them are powered. It should be solid green in normal operation.

Figure 19: Power Indicator LED

There are three LEDs (**Green**) at bottom left of UbiSwitch Baseboard indicating when SFP+ module is plugged to the SFP+ connector. Each LED indicates one SFP+ module at port 0, 9, 10. It should be solid green when SFP+ module is plugged.

Figure 20: SFP+ module Indicator LED

Each Port from 1 to 8 Activity LED is a **Red/Green** dual color LED and each corresponds to a specific port. They indicate activity on each port and will blink when there is traffic on a port. They should be solid off when a port is not connected to any device, and they should blink under normal operation (**Green** blinking indicates a 1000 Mbps connection, **Red** blinking indicates a 100Mbps connection, **Orange** blink indicates a 10Mbps connection). A solid on LED indicates Link/No Activity.

Figure 21: Port 1-8 Link/Activity LEDs

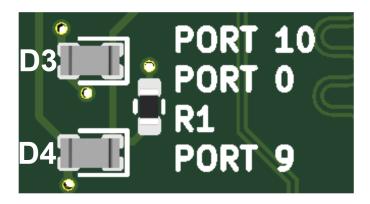

Port 10/0 Activity LED is D4 - **Red/Green** correspondingly. Port 9 activity LED is D3 - **Red**. They should blink under normal operation.

Note that the labeling of these LEDs on the board is incorrect in revision A of the baseboard. This is due to be fixed in revision B of the board.

Figure 22: Port 0,9,10 Activity LEDs

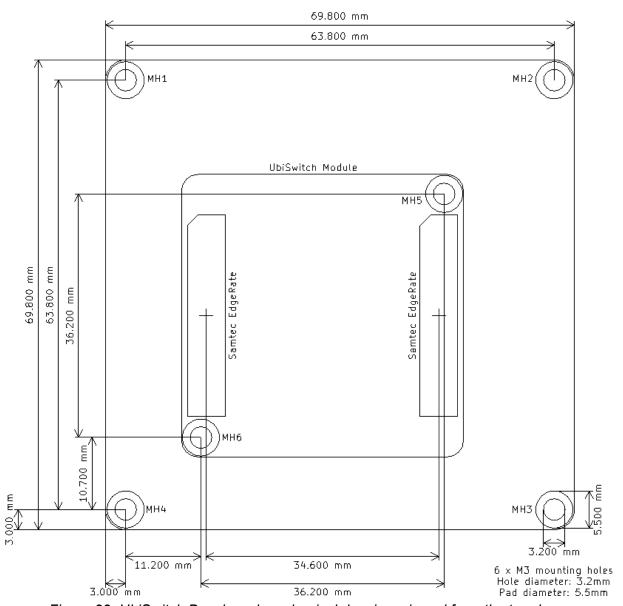

### 2.3.2. Mounting holes

There are six mounting holes on the UbiSwitch Baseboard which are floating by default (not connected to any electrical NET on the board). These holes are designed to accept M3 screws.

Mounting holes 5,6 are used to fix UbiSwitch on UbiSwitch Baseboard.

Mounting holes 1,2,3,4 are used to fix UbiSwitch Baseboard to an enclosure. If external access to the shield ground is required on UbiSwitch Baseboard, mounting hole 3 can be connected to UbiSwitch Baseboard's chassis ground by solder bridge jumper JP1. JP1 is open by default.

# **4 Device Configuration**

UbiSwitch Baseboard itself is a passive board and requires no configuration. For information on how to configure UbiSwitch, please refer to the UbiSwitch Datasheet.

## 5 Mechanical drawing

Figure 22. UbiSwitch Baseboard mechanical drawing, viewed from the top down

Full dimensional drawings and 3D CAD can be found in the links below.

https://botblox.io/content/UbiConn%20Rev%20A%20Dim%20Drawing.pdf https://botblox.io/content/UbiConn%20Rev%20A%20Dim%20Drawing.DXF https://grabcad.com/library/ubiswitch-revision-a-1

# **6 Datasheet Changelog**

| Date       | Datasheet Version | Author      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/02/2023 | A_A               | Josh Elijah | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 09/02/2023 | A_B               | Josh Elijah | Updated 4-pin picoclasp connector to positive locking type                                                                                                                                                                                                                                                                                                                                                                                          |

| 20/07/2023 | A_C               | Josh Elijah | Changed name of board from UbiConn to UbiSwitch BaseBoard to be consistent with website naming. Fixed the power error and reference to 10GBlox in the power characteristics. Fixed pinout error in table 3 (previous datasheet version showed pin P6A_N on pin 23, when it should be 52). Figures were correct. Fixed pinout error in table 2 (previous datasheet version showed C2_LED as pin 24, when it should be pin 34). Figures were correct. |

| 31/07/2023 | A_D               | Josh Elijah | Added note that only 10G SFPs can be used.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10/07/2023 | A_E               | Josh Elijah | Added note about stiff SFP cages                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 25/10/2023 | A_F               | Jaclyn Li   | Table 1.1.2 General Information updated to be correct values                                                                                                                                                                                                                                                                                                                                                                                        |

| 14/11/2023 | A_G               | Josh Elijah | Fixed incorrectly labeled SFP LED indicators                                                                                                                                                                                                                                                                                                                                                                                                        |

## 7 Contact

If you have any questions regarding this product, please contact us:

### info@botblox.org

4 Pavilion Court 600 Pavilion Drive, Northampton Business Park, Northampton, England NN4 7SL

## **8 Certificate of Conformity**

The full text of the Certificate of Conformity of this product is available at the following web address. <a href="https://botblox.io/documentation/">https://botblox.io/documentation/</a>