# **GigaStax Rugged**

# Small 5 port 10/100/1000 Mbps Ethernet Switch

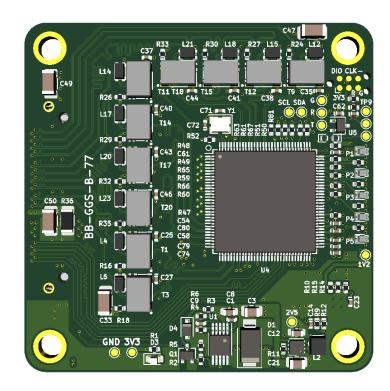

MPN: BB-GGS-B-77

# **Preliminary Datasheet**

October 2023 Board revision B

BotBlox | GigaStax Rugged Datasheet

# Contents

| Contents                                          | 2  |

|---------------------------------------------------|----|

| 1 General Information                             | 3  |

| 1.1 Functionality and Features of GigaStax Rugged | 3  |

| 1.2 Safety Information                            | 5  |

| 1.3 Block Diagram                                 | 6  |

| 1.4 Included Equipment                            | 7  |

| 1.5 RoHS Certification of Compliance              | 7  |

| 2 Hardware Interfaces                             | 8  |

| 2.1 Board Map                                     | 8  |

| 2.2 Connectors and Pinouts                        | 9  |

| 2.3 Other Interfaces                              | 16 |

| 2.4 Daughterboard and Reference Design            | 17 |

| 3 Software Interfaces                             | 20 |

| 4 Device Configuration                            | 20 |

| 4.1 Unmanaged Switch                              | 20 |

| 4.2 Managed Switch                                | 20 |

| 5 Device Characteristics                          | 21 |

| 5.1 Operating Conditions                          | 21 |

| 6 Datasheet Changelog                             | 21 |

| 7 Contact                                         | 21 |

# **1** General Information

## 1.1 Functionality and Features of GigaStax Rugged

GigaStax Rugged is a very small layer 2 unmanaged and managed ethernet switch that fits five 10/100/1000Mbps copper ethernet ports in an ultra-compact 48mm x 48mm form factor. The design of GigaStax Rugged is a modular, stackable board which places 5 ethernet ports onto a Samtec Razor Beam (LSHM-140-03.0-L-DV-A-S-K-TR) stackable header. This allows direct integration of GigaStax Rugged into any daughterboard design, allowing full connector and dimensional flexibility

GigaStax Rugged is designed to be a more rugged and more capable upgrade to our GigaBlox product and is designed for space, weight and price-sensitive (SWaP) industrial, mobile and military applications.

- 1.1.1 Features

- 5 x 10/100/1000M (10/100/1000BASE-T) non-blocking ethernet ports

- Input voltage range from 5 to 60V

- Reverse protected voltage input

- Transient protected voltage input

- -40°C to 85°C Operation Range

- 48mm x 48mm board size

- Samtec RAZOR BEAM<sup>™</sup> connector for power and ports

- Automatic MDI-X crossover

- Unmanaged (out-the-box) functionality

- Embedded STM32L021D4P7 onboard for firmware to implement managed switch functions

- Port Activity Indicators

#### 1.1.2 General Information

| Voltage Input         | 5V to 60V DC (65V absolute max) |

|-----------------------|---------------------------------|

| Voltage Output        | 3.3VDC                          |

| Supported Protocols   | 10/100/1000BASE-T               |

| Number of ports       | 5 x 10/100/1000BASE-T           |

| Packet buffer         | 256kByte                        |

| Power Consumption     | 1W idle, 3.3W at full data rate |

| Weight                | 20 grams                        |

| Size                  | 48mm x 48mm x 8.17mm            |

| Operating Temperature | -40°C to +85°C                  |

| Storage Temperature   | -55°C to +125°C                 |

#### Table 1: General Information

1.1.3 General Operating Instructions

GigaStax Rugged is designed for use in harsh environments, operating from a nominal supply voltage of 24V, but with the ability to operate from as low as 5V and as high as 60V.

A daughterboard needs to be used with GigaStax Rugged to provide access to the ports and power on the board. BotBlox provides standard daughterboard configurations to provide connectivity on Picoblade connectors (**SKU: BB-GSP-B-1**)

To use GigaStax Rugged, first mate the board with a daughterboard then apply an input voltage from 5 to 60V. Then connect external devices and GigaStax Rugged will begin functioning as an unmanaged 10/100/1000Mbit/s network switch.

### 1.2 Safety Information

- This device can operate on voltages near and above 60V. Please read this manual before operating.

- This device is provided "as is". In-application testing prior to integration is recommended.

- This device is provided as an electronic circuit board, and requires integration into chassis for full ingress protection.

- Do not use this product in wet environments without integrating into a chassis.

- Do not operate this product beyond the rated temperature and voltages.

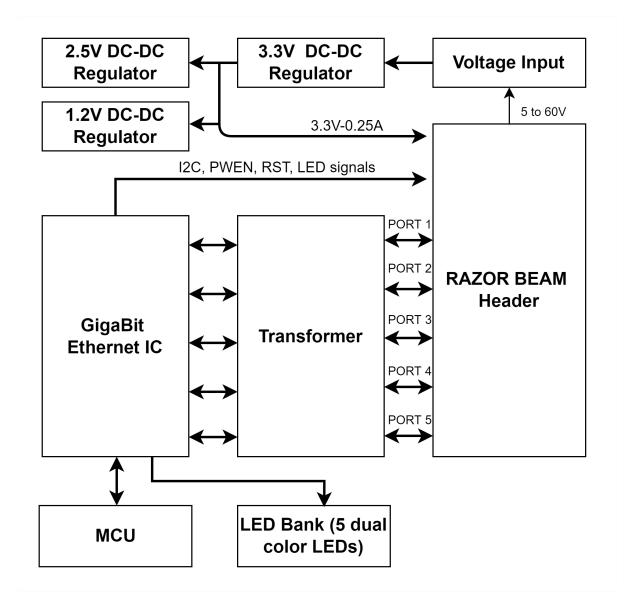

### 1.3 Block Diagram

Figure 1: GigaStax Rugged Block Diagram

### 1.4 Included Equipment

The product includes the following: 1 x GigaStax Rugged board

## 1.5 RoHS Certification of Compliance

GigaStax Rugged complies with the RoHS (Restriction of Hazardous Substances Directive) Certificate of Compliance.

# **2 Hardware Interfaces**

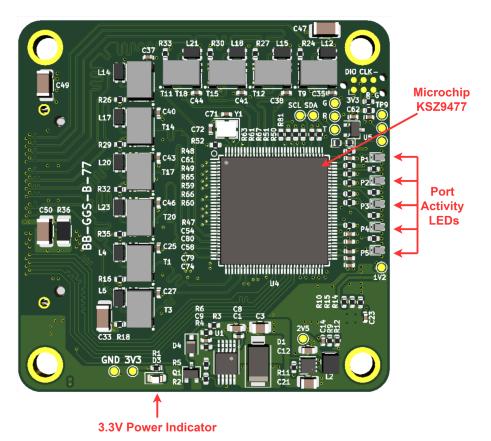

## 2.1 Board Map

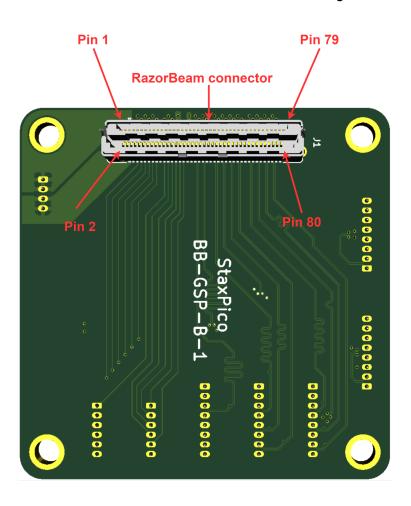

Figure 2: GigaStax Rugged Board Map (front)

Razor beam connector:

- Power supply, power output,

- 10BASE-Te, 100BASE-TX, 1000BASE-T Ethernet Ports (

- PWEN, RESET, I2C, LED signals

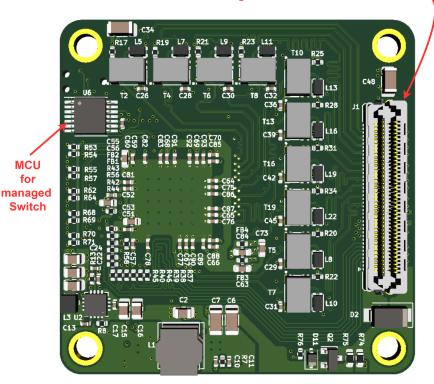

Figure 3: GigaStax Rugged Board Map (back)

### 2.2 Connectors and Pinouts

#### 2.2.1 Razor Beam connector

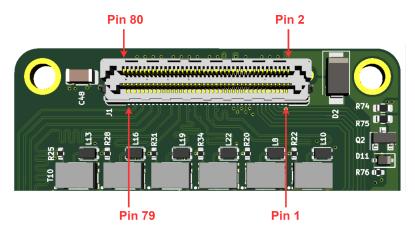

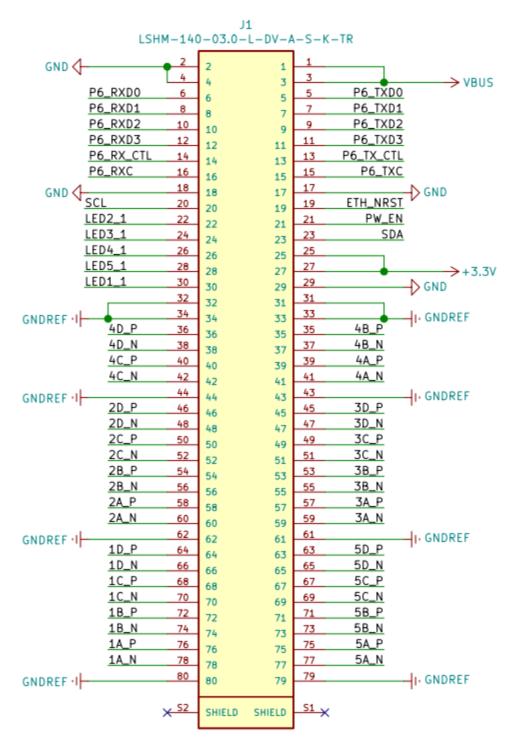

The 5 ports, input voltage, output voltage, RGMII, LED and controls signal are placed onto a Samtec Razor Beam<sup>™</sup> (MPN: LSHM-140-03.0-L-DV-A-S-K-TR) stackable header. The Razor Beam connector on the GigaStax Rugged Board is shown in figure 4 below:

Figure 4: Razor Beam connector

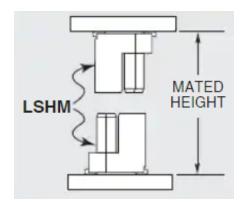

The Razor Beam connector is a hermaphroditic (genderless) connector, meaning the same part is required on the daughtboard for mating. The mating method is shown in figure 5 below.

Figure 5: Razor Beam connector self-mating

The pin mapping between two mated LSHM-140-03.0-L-DV-A-S-K-TR Razor Beam connectors is shown in table 2 below.

| Connector<br>A Pin | Connector<br>B Pin | Connector<br>A Pin | Connector<br>B Pin | Connector<br>A Pin | Connector<br>B Pin |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 1                  | 2                  | 28                 | 27                 | 55                 | 56                 |

| 2                  | 1                  | 29                 | 30                 | 56                 | 55                 |

| 3                  | 4                  | 30                 | 29                 | 57                 | 58                 |

| 4                  | 3                  | 31                 | 32                 | 58                 | 57                 |

| 5                  | 6                  | 32                 | 31                 | 59                 | 60                 |

| 6  | 5  | 33 | 34 | 60 | 59 |

|----|----|----|----|----|----|

| 7  | 8  | 34 | 33 | 61 | 62 |

| 8  | 7  | 35 | 36 | 62 | 61 |

| 9  | 10 | 36 | 35 | 63 | 64 |

| 10 | 9  | 37 | 38 | 64 | 63 |

| 11 | 12 | 38 | 37 | 65 | 66 |

| 12 | 11 | 39 | 40 | 66 | 65 |

| 13 | 14 | 40 | 39 | 67 | 68 |

| 14 | 13 | 41 | 42 | 68 | 67 |

| 15 | 16 | 42 | 41 | 69 | 70 |

| 16 | 15 | 43 | 44 | 70 | 69 |

| 17 | 18 | 44 | 43 | 71 | 72 |

| 18 | 17 | 45 | 46 | 72 | 71 |

| 19 | 20 | 46 | 45 | 73 | 74 |

| 20 | 19 | 47 | 48 | 74 | 73 |

| 21 | 22 | 48 | 47 | 75 | 76 |

| 22 | 21 | 49 | 50 | 76 | 75 |

| 23 | 24 | 50 | 49 | 77 | 78 |

| 24 | 23 | 51 | 52 | 78 | 77 |

| 25 | 26 | 52 | 51 | 79 | 80 |

| 26 | 25 | 53 | 54 | 80 | 79 |

| 27 | 28 | 54 | 53 |    |    |

|    |    |    |    |    |    |

Table 2: Pin matching for mating connector

The signal to pin assignments used on GigaStax Rugged is detailed in table 3 below.

| Pin name | Pin<br>number | Description                                                             |  |

|----------|---------------|-------------------------------------------------------------------------|--|

| GND      | 1             | Ground                                                                  |  |

| GND      | 3             | Ground                                                                  |  |

| GND      | 17            | Ground                                                                  |  |

| GND      | 18            | Ground                                                                  |  |

| GND      | 30            | Ground                                                                  |  |

| VIN      | 2             | Input supply voltage, 5V to 60V                                         |  |

| VIN      | 4             | Input supply voltage, 5V to 60V                                         |  |

| +3V3     | 26            | Output 3.3V, maximum 0.25A                                              |  |

| +3V3     | 28            | Output 3.3V, maximum 0.25A                                              |  |

| GNDREF   | 31            | GND reference for ethernet signals                                      |  |

| GNDREF   | 32            |                                                                         |  |

| GNDREF   | 33            |                                                                         |  |

| GNDREF   | 34            |                                                                         |  |

| GNDREF   | 43            |                                                                         |  |

| GNDREF   | 44            |                                                                         |  |

| GNDREF   | 61            |                                                                         |  |

| GNDREF   | 62            |                                                                         |  |

| GNDREF   | 79            |                                                                         |  |

| GNDREF   | 80            |                                                                         |  |

| P1_A_P   | 75            | Port 1 1000BASE-T Differential Data Pair A ~ D                          |  |

| P1_A_N   | 77            | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs. |  |

| P1_B_P   | 71            |                                                                         |  |

| P1_B_N   | 73            |                                                                         |  |

| P1_C_P | 67 |                                                                                               |  |

|--------|----|-----------------------------------------------------------------------------------------------|--|

| P1_C_N | 69 |                                                                                               |  |

| P1_D_P | 63 |                                                                                               |  |

| P1_D_N | 65 |                                                                                               |  |

| P2_A_P | 57 | Port 2 1000BASE-T Differential Data Pair A ~ D                                                |  |

| P2_A_N | 59 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs.                       |  |

| P2_B_P | 53 |                                                                                               |  |

| P2_B_N | 55 |                                                                                               |  |

| P2_C_P | 49 |                                                                                               |  |

| P2_C_N | 51 |                                                                                               |  |

| P2_D_P | 45 |                                                                                               |  |

| P2_D_N | 47 |                                                                                               |  |

| P3_A_P | 58 | Port 3 1000BASE-T Differential Data Pair A ~ D                                                |  |

| P3_A_N | 60 | Note: 100BASE-TX and 10BASE-Te are also supported on the A and B pairs.                       |  |

| P3_B_P | 54 |                                                                                               |  |

| P3_B_N | 56 |                                                                                               |  |

| P3_C_P | 50 |                                                                                               |  |

| P3_C_N | 52 |                                                                                               |  |

| P3_D_P | 46 |                                                                                               |  |

| P3_D_N | 48 |                                                                                               |  |

| P4_A_P | 40 | Port 4 1000BASE-T Differential Data Pair A ~ D                                                |  |

| P4_A_N | 42 | <ul> <li>Note: 100BASE-TX and 10BASE-Te are also supported on the<br/>and B pairs.</li> </ul> |  |

| P4_B_P | 36 |                                                                                               |  |

| P4_B_N | 38 |                                                                                               |  |

| P4_C_P | 39 |                                                                                               |  |

| P4_C_N41P4_D_P35P4_D_N37P5_A_P76P5_A_N78P5_B_N72P5_B_N74P5_C_P68P5_D_N70P5_D_N66P5_D_N66P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 1P6_RXD311RGMII Port 6 Receive Data bus bit 2P6_RXD415RGMII Port 6 Receive Data bus bit 3P6_RXD311RGMII Port 6 Receive Data bus bit 1P6_RXD415RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RXD415RGMII Port 6 Transmit Data bus bit 1P6_RXD416RGMII Port 6 Transmit Data bus bit 1P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 1P6_TXD312RGMII Port 6 Transmit Data bus bit 1P6_TXC114RGMII Port 6 Transmit Data bus bit 3P6_TX_C1L14RGMII Port 6 125/25/2.5MHz Transmit Clock inputP6_TX_C1L14RGMII Port 6 125/25/2.5MHz Transmit Clock inputP6_TX_C1L14RGMII Port 6 125/25/2.5MHz Transmit Clock inputP6_TX_C114RGMII Port 6 125/25/2.5MHz Transmit Clock input <th></th> <th></th> <th></th>                                                                                                                                                                                               |           |    |                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----|-------------------------------------------------|

| P4_D_N37P4_D_N37P5_A_P76Port 5 1000BASE-T Differential Data Pair A ~ D<br>Note: 100BASE-TX and 10BASE-Te are also supported on the A<br>and B pairs.P5_B_P72P5_B_N74P5_C_P68P5_C_N70P5_D_P64P5_D_N66P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 Receive Control outputP6_RXD17RGMII Port 6 Receive Data bus bit 3P6_RXD29RGMII Port 6 Receive Data bus bit 1P6_RXD311RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 Transmit Data bus bit 0P6_TXD06RGMII Port 6 Transmit Data bus bit 1P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TXCTL14RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL16RGMII Port 6 Transmit ControlP6_TX_CTL16RGMII Port 6 Transmit ControlP6_TX_CTL16RGMII Port 6 Transmit Control </td <td>P4_C_N</td> <td>41</td> <td></td>                                                                                                                                          | P4_C_N    | 41 |                                                 |

| P5_A_P76Port 5 1000BASE-T Differential Data Pair A ~ D<br>Note: 100BASE-TX and 10BASE-Te are also supported on the A<br>and B pairs.P5_B_P72P5_B_N74P5_C_P68P5_C_N70P5_D_N64P5_D_N66P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RXC15RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_RXC10RGMII Port 6 Transmit Data bus bit 1P6_TXD312RGMII Port 6 Transmit Data bus bit 1P6_TXD414RGMII Port 6 Transmit Data bus bit 1P6_TXD412RGMII Port 6 Transmit Data bus bit 1P6_TXD512RGMII Port 6 Transmit Data bus bit 1P6_TXD414RGMII Port 6 Transmit Data bus bit 2P6_TXD512RGMII Port 6 Transmit Data bus bit 3P6_TXC114RGMII Port 6 Transmit ControlP6_TXC216RGMII Port 6 Transmit ControlP6_TXC416RGMII Port 6 Transmit ControlP6_TXC516RGMII Port 6 Tab Porte ControlP6_TXC516RGMII Port 6 Transmit Control <td>P4_D_P</td> <td>35</td> <td></td>                                                                                                                                   | P4_D_P    | 35 |                                                 |

| Note:100BASE-TX and 10BASE-Te are also supported on the A<br>and B pairs.P5_B_P72P5_B_N74P5_C_P68P5_C_N70P5_D_P64P5_D_N66P6_RXD05P6_RXD17P6_RXD29RGMII Port 6 Receive Data bus bit 0P6_RXD311RGMII Port 6 Receive Data bus bit 1P6_RXD311RGMII Port 6 Receive Data bus bit 2P6_RXC415RGMII Port 6 Receive Control outputP6_RXC515RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 1P6_TXD312RGMII Port 6 Transmit Data bus bit 1P6_TXD48RGMII Port 6 Transmit Data bus bit 1P6_TXD510RGMII Port 6 Transmit Data bus bit 1P6_TXD414RGMII Port 6 Transmit Data bus bit 1P6_TXD512P6_TXD414RGMII Port 6 Transmit Data bus bit 1P6_TXC516RGMII Port 6 Transmit Data bus bit 3P6_TXC616RGMII Port 6 Transmit Data bus bit 3P6_TXC716RGMII Port 6 125/25/2.5MHz Transmit Clock inputP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputP6_TXC616P6_TXC716P6_TXC616P6_TXC616P6_TXC7 <td< td=""><td>P4_D_N</td><td>37</td><td></td></td<>                                                                                                                                                                                      | P4_D_N    | 37 |                                                 |

| P5_A_N         78         and B pairs.           P5_B_P         72           P5_B_N         74           P5_C_P         68           P5_C_N         70           P5_D_P         64           P5_D_N         66           P6_RXD0         5           RGMII Port 6 Receive Data bus bit 0           P6_RXD1         7           RGMII Port 6 Receive Data bus bit 1           P6_RXD2         9           RGMII Port 6 Receive Data bus bit 2           P6_RXD3         11           RGMII Port 6 Receive Data bus bit 3           P6_RXC1L         13           RGMII Port 6 Receive Data bus bit 3           P6_RXC2         9           RGMII Port 6 Receive Control output           P6_RXC4         15           RGMII Port 6 Transmit Data bus bit 3           P6_TXD0         6           RGMII Port 6 Transmit Data bus bit 1           P6_TXD1         8           RGMII Port 6 Transmit Data bus bit 2           P6_TXD2         10           RGMII Port 6 Transmit Data bus bit 3           P6_TXD3         12           RGMII Port 6 Transmit Data bus bit 3           P6_TX_CTL         14                                                                                                | P5_A_P    | 76 |                                                 |

| P5_B_N         74           P5_C_P         68           P5_C_N         70           P5_D_P         64           P5_D_N         66           P6_RXD0         5           RGMII Port 6 Receive Data bus bit 0           P6_RXD1         7           RGMII Port 6 Receive Data bus bit 1           P6_RXD2         9           RGMII Port 6 Receive Data bus bit 2           P6_RXD3         11           RGMII Port 6 Receive Data bus bit 3           P6_RX_CTL         13           RGMII Port 6 Receive Data bus bit 3           P6_RX_CTL         13           RGMII Port 6 Receive Control output           P6_RXC         15           RGMII Port 6 Transmit Data bus bit 0           P6_TXD0         6           RGMII Port 6 Transmit Data bus bit 1           P6_TXD1         8           RGMII Port 6 Transmit Data bus bit 2           P6_TXD2         10           RGMII Port 6 Transmit Data bus bit 2           P6_TXD3         12           RGMII Port 6 Transmit Data bus bit 3           P6_TXD3         12           RGMII Port 6 Transmit Data bus bit 3           P6_TX_CTL         14           RGMII                                                                              | P5_A_N    | 78 |                                                 |

| P5_C_P         68           P5_C_N         70           P5_D_P         64           P5_D_N         66           P6_RXD0         5           RGMII Port 6 Receive Data bus bit 0           P6_RXD1         7           RGMII Port 6 Receive Data bus bit 1           P6_RXD2         9           RGMII Port 6 Receive Data bus bit 2           P6_RXD3         11           RGMII Port 6 Receive Data bus bit 3           P6_RX_CTL         13           RGMII Port 6 Receive Control output           P6_RXC         15           RGMII Port 6 Transmit Data bus bit 0           P6_RXD1         8           RGMII Port 6 Transmit Data bus bit 1           P6_RXC         15           RGMII Port 6 Transmit Data bus bit 0           P6_TXD1         8           RGMII Port 6 Transmit Data bus bit 1           P6_TXD1         8           RGMII Port 6 Transmit Data bus bit 1           P6_TXD2         10           RGMII Port 6 Transmit Data bus bit 3           P6_TXD3         12           RGMII Port 6 Transmit Data bus bit 3           P6_TX_CTL         14           RGMII Port 6 Transmit Control           P6_TX_                                                                    | P5_B_P    | 72 |                                                 |

| P5_C_N         70           P5_D_P         64           P5_D_N         66           P6_RXD0         5         RGMII Port 6 Receive Data bus bit 0           P6_RXD1         7         RGMII Port 6 Receive Data bus bit 1           P6_RXD2         9         RGMII Port 6 Receive Data bus bit 2           P6_RXD3         11         RGMII Port 6 Receive Data bus bit 3           P6_RX_CTL         13         RGMII Port 6 Receive Control output           P6_RXC         15         RGMII Port 6 Transmit Data bus bit 0           P6_TXD0         6         RGMII Port 6 Transmit Data bus bit 1           P6_RXC         15         RGMII Port 6 Transmit Data bus bit 1           P6_TXD1         8         RGMII Port 6 Transmit Data bus bit 1           P6_TXD2         10         RGMII Port 6 Transmit Data bus bit 1           P6_TXD3         12         RGMII Port 6 Transmit Data bus bit 2           P6_TXD3         12         RGMII Port 6 Transmit Data bus bit 3           P6_TX_CTL         14         RGMII Port 6 Transmit Control           P6_TXC         16         RGMII Port 6 125/25/2.5MHz Transmit Clock input           SDA         24         I2C SDA Data In/Out | P5_B_N    | 74 |                                                 |

| P5_D_P64P5_D_N66P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 1P6_TXD18RGMII Port 6 Transmit Data bus bit 2P6_TXD210RGMII Port 6 Transmit Data bus bit 3P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA2412C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P5_C_P    | 68 |                                                 |

| P5_D_N66P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 2P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TXC16RGMII Port 6 Transmit Data bus bit 3P6_TXC16RGMII Port 6 Transmit Data bus bit 3P6_TXC16RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 Transmit Control                                                                                                                                                                                                                                                                                                                                                               | P5_C_N    | 70 |                                                 |

| P6_RXD05RGMII Port 6 Receive Data bus bit 0P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 2P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P5_D_P    | 64 |                                                 |

| P6_RXD17RGMII Port 6 Receive Data bus bit 1P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P5_D_N    | 66 |                                                 |

| P6_RXD29RGMII Port 6 Receive Data bus bit 2P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P6_RXD0   | 5  | RGMII Port 6 Receive Data bus bit 0             |

| P6_RXD311RGMII Port 6 Receive Data bus bit 3P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P6_RXD1   | 7  | RGMII Port 6 Receive Data bus bit 1             |

| P6_RX_CTL13RGMII Port 6 Receive Control outputP6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P6_RXD2   | 9  | RGMII Port 6 Receive Data bus bit 2             |

| P6_RXC15RGMII Port 6 125/25/2.5MHz Receive Clock outputP6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P6_RXD3   | 11 | RGMII Port 6 Receive Data bus bit 3             |

| P6_TXD06RGMII Port 6 Transmit Data bus bit 0P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P6_RX_CTL | 13 | RGMII Port 6 Receive Control output             |

| P6_TXD18RGMII Port 6 Transmit Data bus bit 1P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P6_RXC    | 15 | RGMII Port 6 125/25/2.5MHz Receive Clock output |

| P6_TXD210RGMII Port 6 Transmit Data bus bit 2P6_TXD312RGMII Port 6 Transmit Data bus bit 3P6_TX_CTL14RGMII Port 6 Transmit ControlP6_TXC16RGMII Port 6 125/25/2.5MHz Transmit Clock inputSDA24I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P6_TXD0   | 6  | RGMII Port 6 Transmit Data bus bit 0            |

| P6_TXD3       12       RGMII Port 6 Transmit Data bus bit 3         P6_TX_CTL       14       RGMII Port 6 Transmit Control         P6_TXC       16       RGMII Port 6 125/25/2.5MHz Transmit Clock input         SDA       24       I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P6_TXD1   | 8  | RGMII Port 6 Transmit Data bus bit 1            |

| P6_TX_CTL       14       RGMII Port 6 Transmit Control         P6_TXC       16       RGMII Port 6 125/25/2.5MHz Transmit Clock input         SDA       24       I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P6_TXD2   | 10 | RGMII Port 6 Transmit Data bus bit 2            |

| P6_TXC     16     RGMII Port 6 125/25/2.5MHz Transmit Clock input       SDA     24     I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P6_TXD3   | 12 | RGMII Port 6 Transmit Data bus bit 3            |

| SDA 24 I2C SDA Data In/Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P6_TX_CTL | 14 | RGMII Port 6 Transmit Control                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P6_TXC    | 16 | RGMII Port 6 125/25/2.5MHz Transmit Clock input |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SDA       | 24 | I2C SDA Data In/Out                             |

| SCL 19 I2C SCL serial clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SCL       | 19 | I2C SCL serial clock                            |

| ETH_NRST | 20 | Active low system reset                                                                                            |  |

|----------|----|--------------------------------------------------------------------------------------------------------------------|--|

| PW_EN    | 22 | GigaStax power control. Low logic (Ven < 0.5V) or Floating (Default) is enable. High logic (Ven > 1.4V) is disable |  |

| LED1_1   | 29 | Port 1 LED Indicator 1                                                                                             |  |

| LED2_1   | 21 | Port 2 LED Indicator 1                                                                                             |  |

| LED3_1   | 23 | Port 3 LED Indicator 1                                                                                             |  |

| LED4_1   | 25 | Port 4 LED Indicator 1                                                                                             |  |

| LED5_1   | 27 | Port 5 LED Indicator 1                                                                                             |  |

Table 3: GigaStax Rugged connector pin assignments

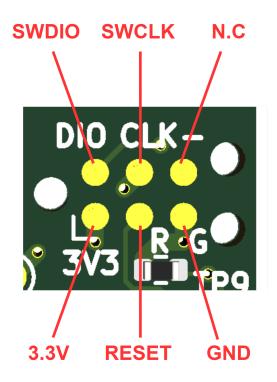

#### 2.2.2 SWD Programming Header

A programming header on the front of the board allows the STM32L021D4P7 on GigaStax Rugged to be programmed over SWD.

*Figure 6: SWD programming header pinout*

This header allows access to the SWD port on the onboard STM32 microcontroller, and requires the use of a 6-pin needle adapter such as the <u>J-Link 6-pin needle adapter</u> along with an in-circuit programmer such as the <u>J-Link</u>.

### 2.3 Other Interfaces

There are six LEDs on GigaStax Rugged in total. Five of these LEDs are dual colour LEDs, meaning there are a total of eleven LED signals on this board. Five of the LED signals can be taken off board.

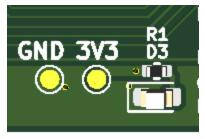

The 3.3V Power Indicator LED (**Green**) indicates that voltage is present on the 3.3V line. It should be solid green in normal operation.

Figure 7: Power Indicator LED

Each Port Activity LED is a **Red/Green** dual color LED and each corresponds to a specific port. They indicate activity on each port and will blink when there is traffic on a port. They should be solid off when a port is not connected to any device, and they should blink under normal operation (**Green** blinking indicates a 1000 Mbps connection, **Red** blinking indicates a 100Mbps connection, **Orange** blink indicates a 10Mbps connection). A solid on LED indicates Link/No Activity.

Figure 8: Port Activity Dual Red/Yellow-Green LED

### 2.4 Daughterboard and Reference Design

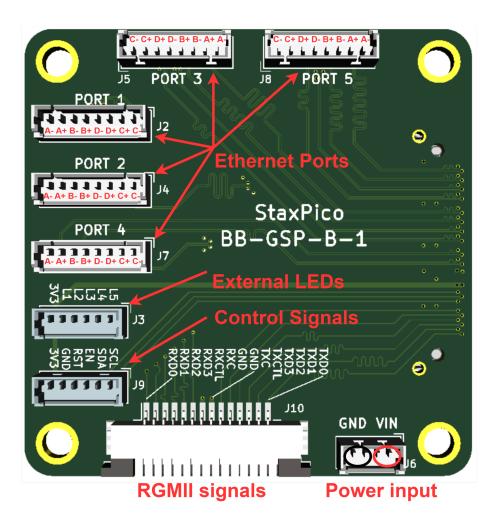

BotBlox provides a Daughterboard - the StaxPico for use with GigaStax Rugged.

#### 2.4.1 StaxPico (GigaStax Picoconn Daughterboard)

GigaStax Picoconn is a simple breakout board for GigaStax Rugged that routs the 5 ports, I2C, control signals and Power to Molex Pico-Blade connectors; RGMII signals to FFC connector

Figure 9: GigaStax Rugged PicoConn Board Map (front)

Figure 10: GigaStax Rugged PicoConn Board Map (back)

The mapping of Port and Power connectors is identical to the mapping used on our GigaBlox board, thus the cables can be used interchangeably with GigaBlox.

GigaStax Rugged Picoconn exposes RGMII on a FFC connector, this allows two boards to be connected to form a 10 port switch. The connector used on the board is <u>1-84953-4</u>, which mates with 14 position FFC cable <u>0151670291</u>.

An External LED header allows port activity indicator signals can be brought off - board for integration into a chassis. The LED signals are provided in a common anode configuration. The anode of all external LEDs should connect to the 3.3V on the External LED header, and the cathode of the external LED should connect to the corresponding "Lx" connection on the header.

The connector used on the board for LED signals and Control signals is <u>530470610</u>, which mates with Cable assembly <u>0151340603</u> or housing <u>0510210600</u>. 2.4.2 Reference design for the Razor Board connector on daughterboard

Figure 11 below shows the correct signal mapping to use on any daughterboard for GigaStax Rugged.

Figure 11: RAZOR BEAM connector on Daughterboard

# **3 Software Interfaces**

There is currently no software interface on GigaStax Rugged. It functions solely as an unmanaged switch.

# **4 Device Configuration**

### 4.1 Unmanaged Switch

To use GigaStax Rugged in an unmanaged application requires no configuration. Simply connect a voltage to the voltage input and connect downstream devices.

### 4.2 Managed Switch

Operating GigaStax Rugged as a managed switch is not possible at present.

# **5 Device Characteristics**

### 5.1 Operating Conditions

5.1.1 Absolute Maximum Ratings

Operating in these ranges will reduce the lifetime of the device.

| Voltage Input Maximum | 65V          |

|-----------------------|--------------|

| Storage Temperature   | -55°C +125°C |

| Operating Temperature | -40°C +85°C  |

# **6 Datasheet Changelog**

| Date       | Datasheet Version | Author      | Notes                                                                                                    |

|------------|-------------------|-------------|----------------------------------------------------------------------------------------------------------|

| 18/02/2022 | A_A               | Josh Elijah | Initial release                                                                                          |

| 26/10/2023 | A_B               | Jaclyn Li   | Table 1.1.2 General Information and<br>Table 5.1.1 Operating Conditions<br>updated to be correct values. |

# 7 Contact

If you have any questions regarding this product, please contact us:

info@botblox.org

4 Pavilion Court 600 Pavilion Drive, Northampton Business Park, Northampton, England NN4 7SL

BotBlox | GigaStax Rugged Datasheet

# **8 Certificate of Conformity**

The full text of the Certificate of Conformity of this product is available at the following web address. <u>https://botblox.io/documentation/</u>